HPC Prozessoren und Beschleuniger

Im Rahmen der Europäischen Forschungsinitiative "European Processor Initiative" (EPI) entwickeln wir gemeinsam mit unseren Partnern hochperformante Architekturen für High Performance Computing (HPC) Prozessoren und applikationsspezifische Beschleuniger. Ziel dieser Entwicklungen ist es, anspruchsvolle Rechenanwendungen für Exascale-Computer auf besonders energieeffiziente Weise zu ermöglichen (1ExaFLOPS=10^18 Gleitkommaoperationen pro Sekunde).

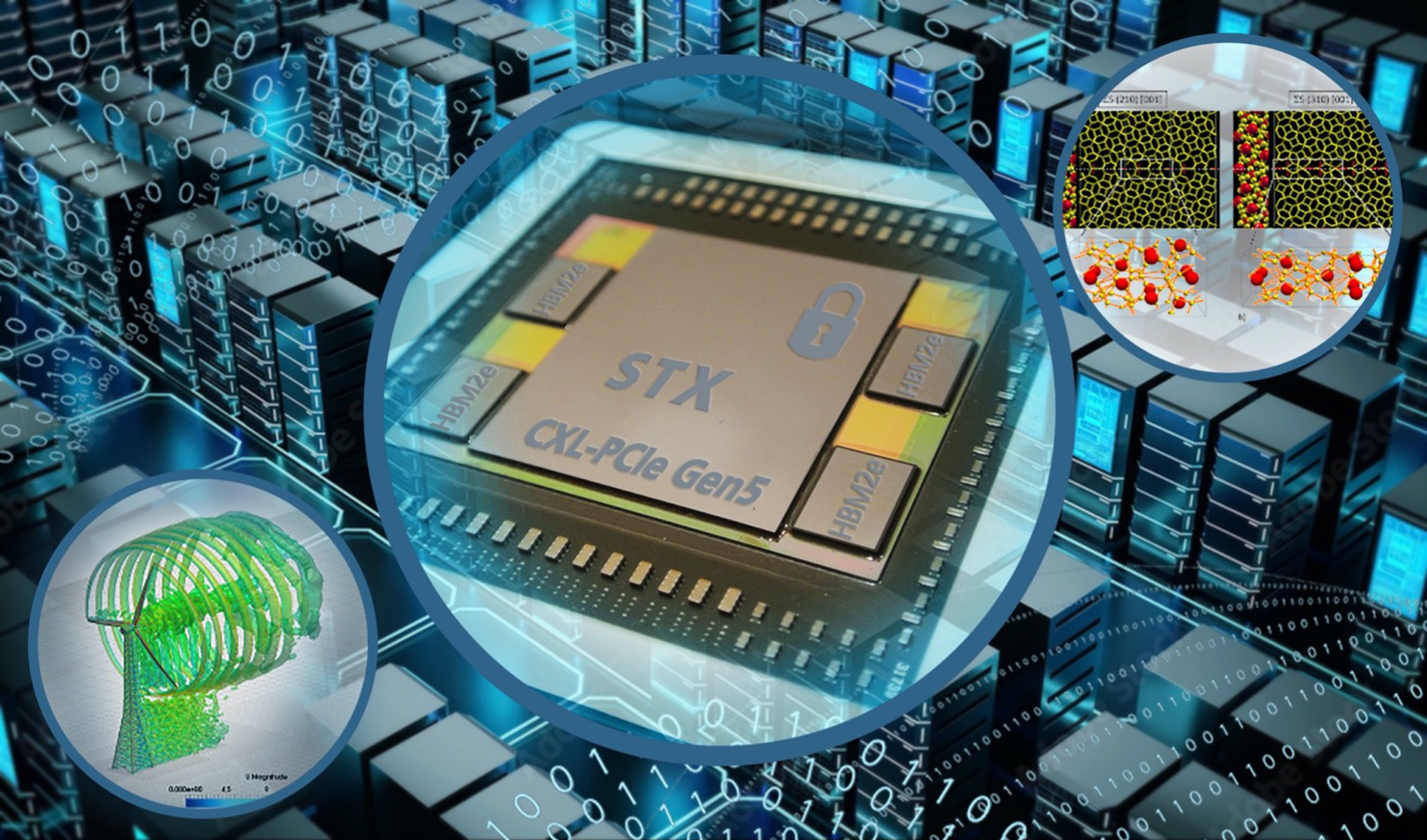

STX Stencil- und Tensor-Beschleuniger als Chiplet

In Zusammenarbeit mit dem Fraunhofer-Institut für Techno- und Wirtschaftsmathematik (ITWM), der ETH Zürich, EXTOLL und weiteren Partnern realisieren wir hocheffiziente SoC-Architekturen für 2D und 3D Stencil-basierte Applikationen. Dafür wurde eine speziell optimierte Stencil-Processing-Unit mit Unterstützung von RISC-V Prozessoren entwickelt. Diese Architektur ist nicht nur in der Rechenleistung skalierbar, sie verbraucht bei identischer Rechenleistung auch nur einen Bruchteil der Energie im Vergleich zu kommerziell verfügbaren HPC-Prozessoren oder GPUs.

Basierend auf solchen Architekturen entwickeln wir skalierbare, kunden- und anwendungsspezifische Beschleuniger, die einfach zu programmieren sind, extrem hohe Performance und Energieeffizienz bieten und als rein europäische Lösungen ein hohes Maß an Technologie-Souveränität repräsentieren.

Anwendungen

- Maschinelles Lernen mit CNNs (Convolutional Neural Networks)

- Strömungs- und Wellensimulationen

- Wetter- und Klimasimulationen

- Big Data-Analysen

- Datenflussoptimierungen in Datencentern

- Materialforschung

- Seismische Explorationen