First-Time-Right-Entwürfe bei viel kürzeren Entwicklungszeiten

Erlangen/Dresden, 20. April 2015: Der am Institutsteil Entwurfsautomatisierung des Fraunhofer-Instituts für Integrierte Schaltungen IIS entwickelte »Intelligent IP Mixed-Signal-Designflow« bietet einen einzigartigen Automatisierungsgrad, insbesondere für den sonst sehr zeitaufwendigen und fehleranfälligen Analogentwurf.

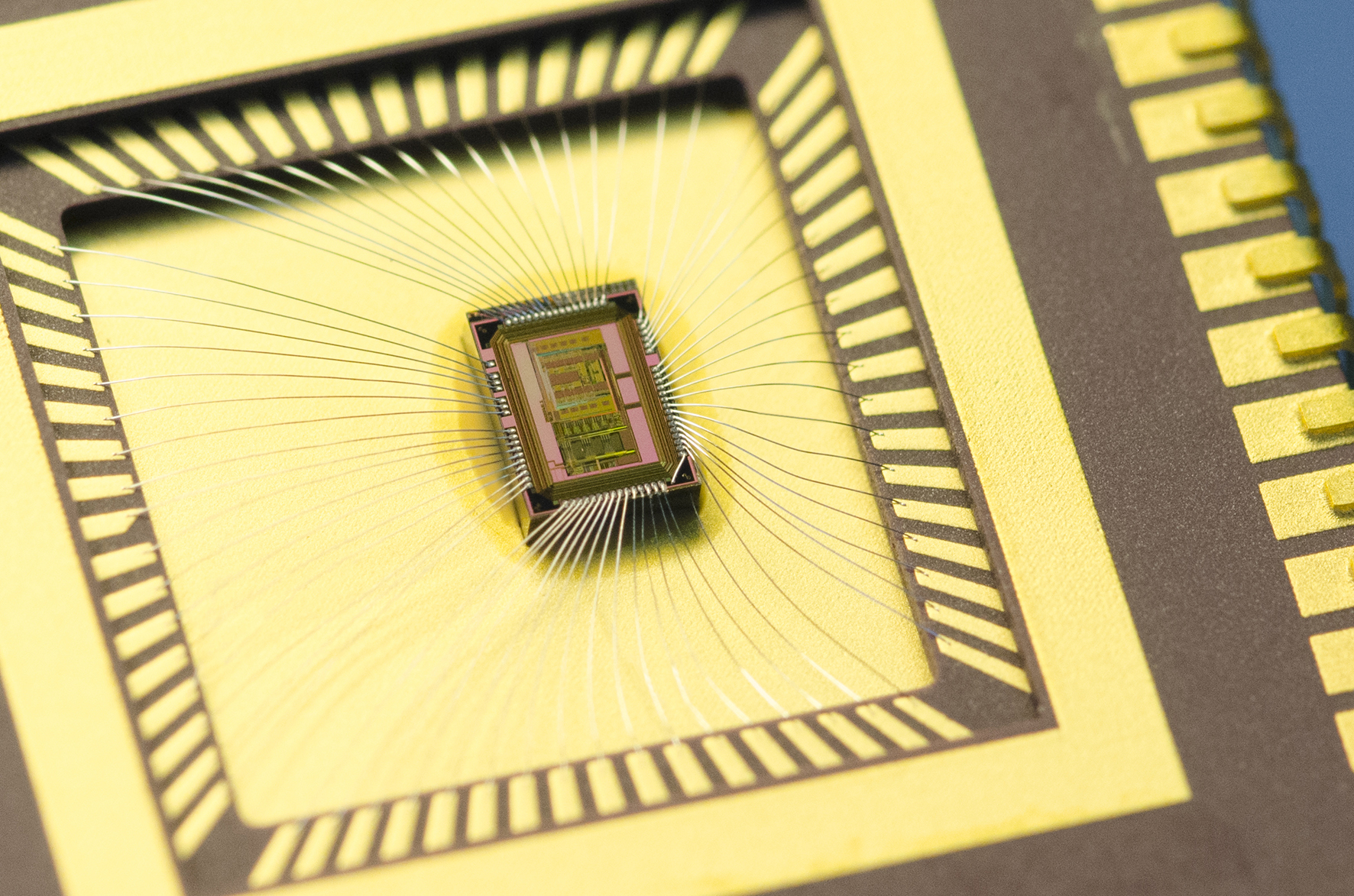

Integrierte Schaltungen mit digitalen und analogen Anteilen, sogenannte Mixed-Signal-ICs, sind heute in unzähligen mikroelektronischen Produkten dominant, z. B. in Konsumgütern, sicherheitskritischen Anwendungen im Automobil, in der Medizintechnik oder der Raumfahrt. Der Analogteil nimmt dabei meist nicht mehr als 20 Prozent der Chipfläche ein, verursacht aber durch einen geringen Grad an Entwurfsautomatisierung hohe Entwicklungskosten und Entwurfsrisiken. Dieses Problem verschärft sich mit zunehmender Miniaturisierung in den Halbleitertechnologien. Der am Institutsteil Entwurfsautomatisierung des Fraunhofer IIS entwickelte »Intelligent IP Mixed-Signal-Designflow« bietet jetzt einen einzigartigen Automatisierungsgrad, insbesondere für den sonst sehr zeitaufwendigen und fehleranfälligen Analogentwurf.

Integrierte Schaltungen kostengünstig, schnell und zuverlässig

In mehreren Entwicklungsprojekten ist es den Designingenieuren des Fraunhofer IIS gelungen, eine deutliche Effizienzsteigerung mit Hilfe des Intelligent IP Mixed-Signal-Designflows nachzuweisen. 40 Prozent Kosten- und Zeitersparnis konnten zum Beispiel bei dem Entwurf eines multiphysikalischen SMART Sensor-ASICs erreicht werden – es entstanden verschiedene ASICs für unterschiedliche Anforderungen mit nur einmaligem Entwicklungsaufwand. Zukünftig wird durch automatische Architekturauswahl im Systemdesign die Effizienz noch weiter steigen. Weiterhin wurde der neuartige Designflow erfolgreich unter anderem in industriellen Entwürfen von hochauflösenden A/D-Wandlern sowie für den Entwurf eines extrem schnellen Bildsensors eingesetzt. Johann Hauer, Leiter der Mixed-Signal-ASIC-Entwicklung am IIS, schwärmt: »Automatisierung im Analogentwurf wünschen wir uns seit Jahren, aber dieser komplette

Designflow erfüllt erstmals die versprochenen Vorteile für unseren Entwurfsalltag.

40 Prozent Zeiteinsparung und die hohe Designsicherheit heißen für uns, dass wir endlich First-Time-Right-Entwürfe bei viel kürzeren Entwicklungszeiten anbieten können. Entscheidend ist auch die sehr gute Akzeptanz bei unseren Designingenieuren durch die intuitive Handhabung.« Schon jetzt können Kunden, in deren Auftrag die Fraunhofer-Ingenieure Mixed-Signal-ASICs und -IPs entwickeln, profitieren – ab 2016 wird der Intelligente IP-Designflow auch beim Kunden einsetzbar sein.

Einmaliger Designaufwand für viele Anwendungen und verschiedene Technologien

Derzeit unterstützt der Designflow etablierte Fertigungstechnologien von 350 nm bis 28 nm Strukturgröße verschiedenster Hersteller. Die Weiterentwicklung für zukünftige Ultra-Low-Power Technologien kleiner 28 nm wird bereits in Forschungsvorhaben vorangetrieben. Demonstriert wird sie in mikroelektronischen Systemen für sicherheitsrelevante Automobilanwendungen sowie für die Kabinenkommunikation in der Luftfahrt.