Anwendungen mit Sensoren und Treibern erfordern analoge und Mixed-Signal-Frontends. Wir entwickeln nach den Anforderungen unserer Kunden High-Performance ASICs inklusive Analog-Digital-/ Digital-Analog-Umsetzer und Power-Management-Schaltungen. Wir verbinden Ihre Sensoren mit der digitalen Welt.

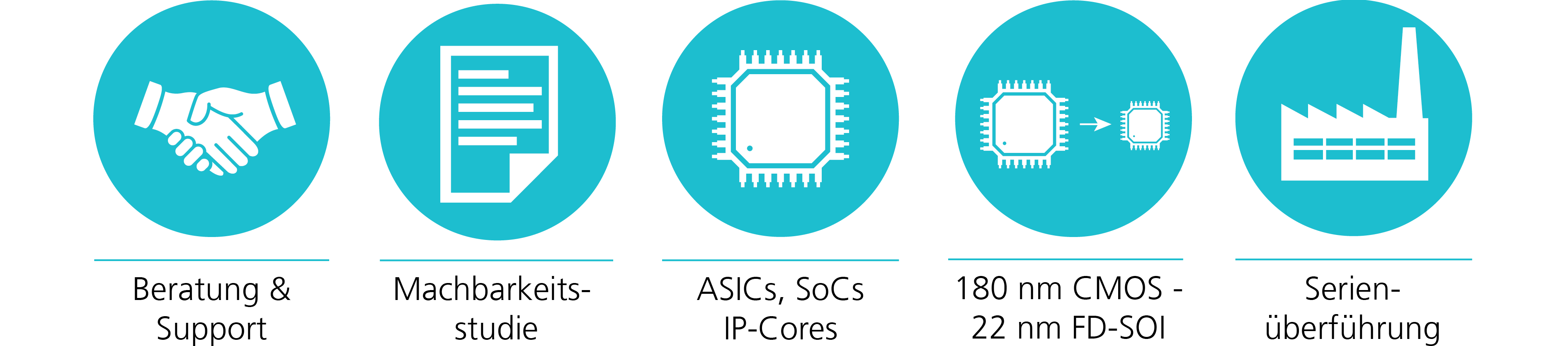

Wir unterstützen unsere Kunden bei der Auswahl der am besten geeigneten Halbleitertechnologie: Ob kostengünstige Standard-CMOS oder fortschrittliche, schnelle und energiesparende 22 nm FDSOI-Technologie.

Als unabhängiges Designhaus mit Analog als auch Digital IC-Design-Teams können wir für jede Anwendung die nach technischen sowie wirtschaftlichen Kriterien beste Technologie auswählen.