Was ist neuromorphe Hardware?

Neuromorphe Hardware basiert auf spezialisierten Rechnerarchitekturen, die die Struktur (Morphologie) neuronaler Netze (NN) von Grund auf widerspiegeln: Dedizierte Verarbeitungseinheiten bilden direkt in der Hardware die Funktionsweise von Neuronen nach, zwischen denen ein physisches Verbindungsnetz (Bus-System) für den schnellen Austausch von Informationen sorgt. Dieses Konzept ist prinzipiell vom menschlichen Gehirn inspiriert, wo biologische Neuronen und Synapsen in ähnlicher Weise zusammenarbeiten. Spezialisierte neuromorphe Einheiten sind zwar weniger flexibel als klassische Mehrzweckprozessoren (CPUs), dafür aber außerordentlich leistungsfähig und energieeffizient im Einsatz für Training und Inferenz von tiefen neuronalen Netzen (Deep Neural Networks, DNNs).

Warum neuromorphe Hardware?

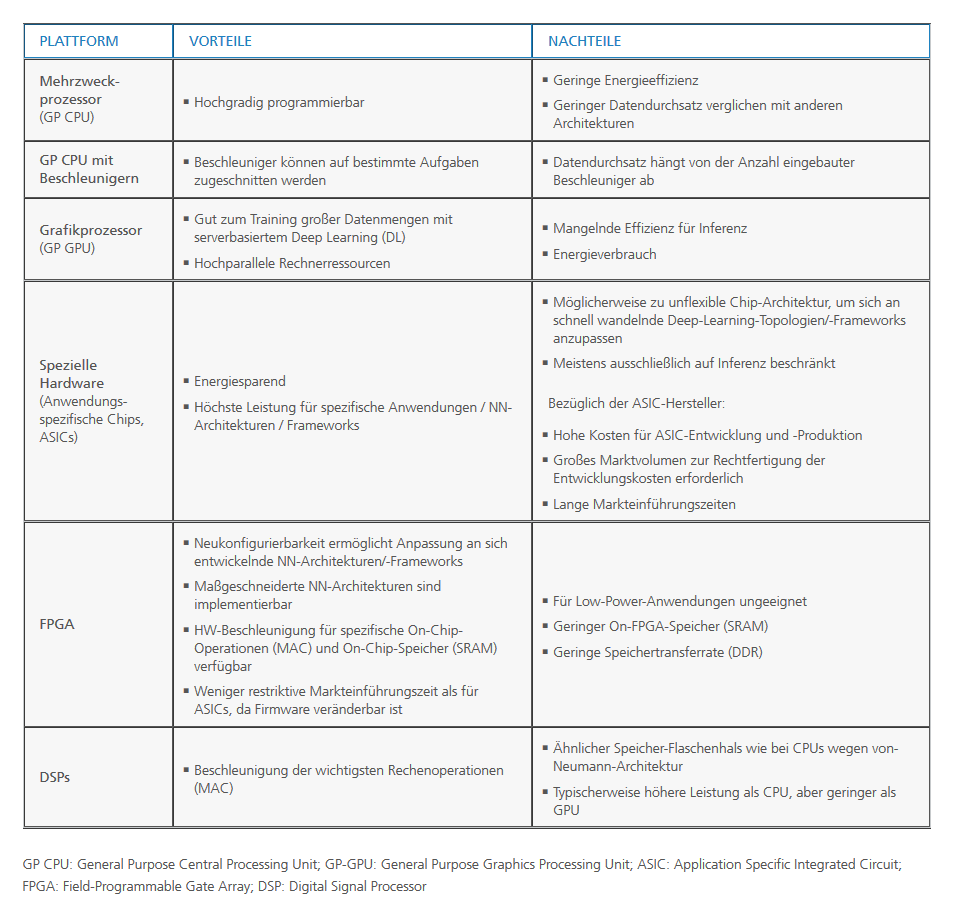

Klassische Computer basieren auf einer sogenannten Von-Neumann-Architektur, in der Prozessorkerne sequenziell Befehle ausführen und dabei die Daten im zentralen Speicher bearbeiten. Das heißt, die Rechenleistung der Computersysteme ist abhängig von der Datenübertragungsrate zwischen Prozessor und Speicher. Man spricht hier vom »Von-Neumann-Flaschenhals«. Mit zunehmend anspruchsvolleren Anwendungen haben sich deshalb Hochleistungsrechner mit Multi-Core-Architekturen durchgesetzt, die Berechnungen hochgradig parallelisiert ausführen können. Tatsächlich aber sind die Möglichkeiten, Berechnungen zu parallelisieren, durch den Zugriff auf gemeinsame Speicherressourcen immer zu einem gewissen Grad limitiert. Neueste Fortschritte im Bereich Deep Learning fordern diese Einschränkungen besonders heraus, weil die hochgradig parallelisierte Struktur tiefer neuronaler Netze ganz spezifisch verteilte Speicherzugriffsmuster erfordert. Solche Zugriffsmuster können mit herkömmlicher Computertechnologie kaum effizient abgebildet werden. Neuromorphe Hardware geht diese Herausforderung an und hilft dabei, Geräten und Systemen künstlichen Intelligenz (KI) zur verleihen.