Datenrate vervierfacht - 3D-Chip für Ultra-HD-Kameras

Im Projekt Memory³ ist es den Forschern des Fraunhofer IIS/EAS gelungen, die Breite der Leitungen zwischen Prozessor und Speicher so stark zu reduzieren, dass sich die Leistungsfähigkeit des Systems vervierfacht hat. Für die Elektronik von Ultra-HD-Kameras und andere leistungsintensive Bauteile kommt die neue, dreidimensionale Integrationstechnologie einem Quantensprung gleich.

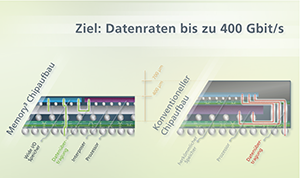

Kleiner ist besser. Bei elektronischen Chips ist dies der Regelfall. Mittlerweile aber stoßen klassische Aufbauten mit standardisierten Bauteilgrößen an ihre Grenzen. Soll gleichzeitig ihre Leistungsfähigkeit erweitert werden, können sie kaum noch winziger werden. Ein augenfälliges Beispiel ist die Elektronik von Ultra-HD-Kameras, die viermal mehr Bildpunkte aufnehmen als Kameras mit Full-HD-Auflösung. Um die dabei entstehenden Datenmengen energiesparend und auf kleinem Raum zu verarbeiten, muss die Anordnung von Prozessor und dem Wide-I/O-Speicher auf der Leiterplatte neu und dreidimensional gedacht werden.

Genau diese Idee hat das Team um Andy Heinig vom Institutsteil Entwurfsautomatisierung EAS des Fraunhofer-Instituts für Integrierte Schaltung IIS umgesetzt. Für das Projekt Memory3 haben sie einen Chipaufbau entwickelt, der den Hochleistungs-Anforderungen von Ultra-HD-Kameras gerecht wird. »Unser 3D-integrierter Aufbau führt zu kürzeren Leitungen zwischen den Komponenten. Deshalb werden Bild- und Toninformationen deutlich schneller übertragen«, erklärt Heinig. So ist eine Datenrate von 400 GBit/s möglich. Das entspricht dem Vierfachen des bislang Möglichen.

Der »Clou« des neuen Chips ist eine Reduktion der Leitungsbreite: Prozessor und Speicher sind im selben Gehäuse angeordnet. Dazwischen arbeitet eine dünne Trägerschicht (Interposer) als Datenleitung. Durch diese hochfeine Leitungsstruktur können Prozessor und Speicher so dicht »zusammenwachsen«, dass sich der Datenaustausch deutlich beschleunigt und der Energieverbrauch senkt. »Lag der Abstand zwischen den Chips ursprünglich im Millimeterbereich, arbeiten wir nun deutlich unter einem Millimeter«, betont Heinig.

Rund eineinhalb Jahre haben die Experten des Fraunhofer IIS für die theoretische Entwicklung und den Bau eines Prototyps benötigt. Der Entwicklungspartner Dream Chip Technologies hatte das Team vor allem im Bereich der Applikationen unterstützt. Ende Februar wird das Projekt Memory3 nun abgeschlossen. »Wir gehen allerdings davon aus, dass wir mit dieser Entwicklung das Ende der Fahnenstange längst noch nicht erreicht haben«, sagt Heinig. Weitere, deutliche Leistungssprünge um den Faktor Vier oder höher seien in den kommenden Jahren durchaus möglich.

Zudem ist der aktuelle Aufbau des 3D-Mikrochips vor allem in Hinblick auf Ultra-HD-Kameras entwickelt. Er kann aber künftig auch in anderen Bereichen wie etwa bei Grafikkarten oder Vermittlungsknoten von Glasfasernetzen eingesetzt werden.

Das Projekt Memory3 wurde vom Bundesministerium für Wirtschaft und Energie im Rahmen des Zentralen Innovationsprogramms Mittelstand (ZIM) unterstützt.