Benötigen Sie langfristig verfügbare hohe Funktionalität, Zuverlässigkeit und Performance Ihres Systems? Dann sind anwendungsspezifische integrierte Schaltungen (ASICs) die optimale Lösung! Denn ASICs bieten in vielen Anwendungen entscheidende Vorteile gegenüber diskreten Lösungen mit Standardkomponenten. Sie ermöglichen geringe Systemkosten, schützen effektiv vor Plagiaten und sichern so Ihr eigenes Know-How.

Gerade für mittelständische Unternehmen ist ein deutlich anderer Entwicklungsablauf für ASICs im Gegensatz zu diskreter Elektronik eine große Hürde. Die Entwicklung und Fertigung von Prototypen dauert wesentlich länger und eine Korrektur mit dem Lötkolben ist nicht möglich. Für den fehlerfreien Schaltungsentwurf werden unter anderem Expertenwissen und komplexe Software-Tools benötigt.

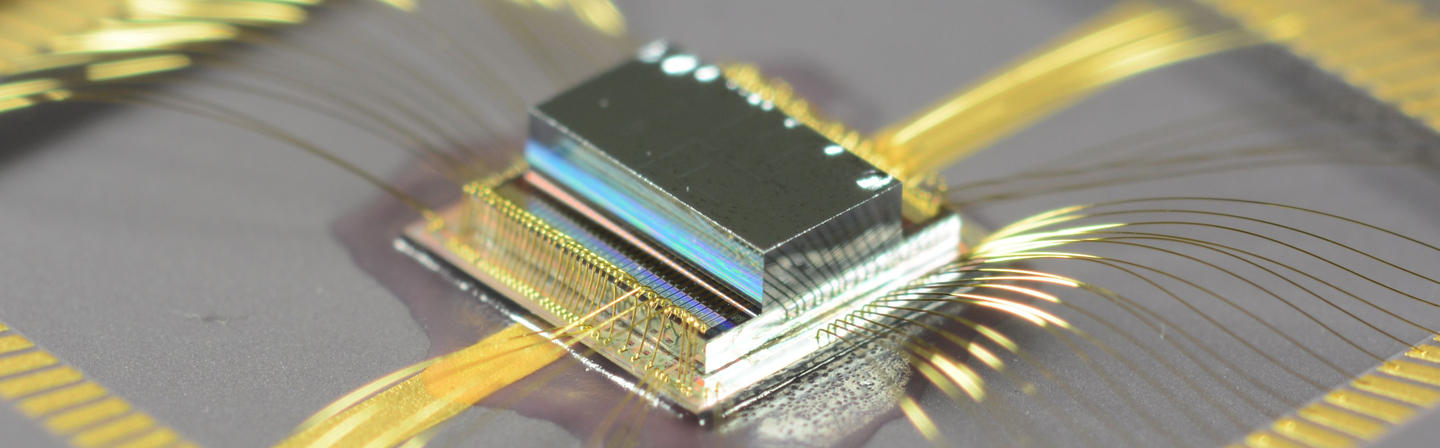

In diesem Workshop präsentiert das Fraunhofer IIS mit seinen beiden Kooperationspartnern, ams und RoodMicrotec, seine Kompetenzen und Leistungen, mit denen es seine Kunden gemeinsam bei der ASIC-Entwicklung von der Idee bis zum qualifizierten Serienprodukt begleitet:

- ams als Halbleiter-Hersteller mit zuverlässigen CMOS-Prozessen (180 nm und 350 nm),

- das Fraunhofer IIS als Entwickler anwendungsspezifischer integrierter Schaltungen und Systeme,

- RoodMicrotec als Anbieter von Testlösungen, Qualifikationen nach etablierten Standards, Supply Chain Management sowie Technologie- und Fehleranalyse (RMA - Return Material Analysis).

Der Workshop richtet sich an Produktmanager, Geschäftsführer, Entwickler und QM-Beauftragte.