Röntgenbildgebung unterstützt bei der frühzeitigen Detektion konstruktiver Schwachstellen bei Halbleitern

Technische Bauteile erfahren eine stetige Miniaturisierung, werden gleichzeitig jedoch zunehmend leistungsstärker. Vor allem Halbleiter-Komponenten und insbesondere jene, welche für den Einsatz im Automotive-Bereich ausgelegt sind, laufen Gefahr, starken Strompulsen ausgesetzt zu sein. Um auch bei solch hochtechnologisierten Bestandteilen größtmögliche Ausfallsicherheit und Langlebigkeit gewährleisten zu können, unterziehen Hersteller Prototypen vor dem Markstart ausgiebigen Tests.

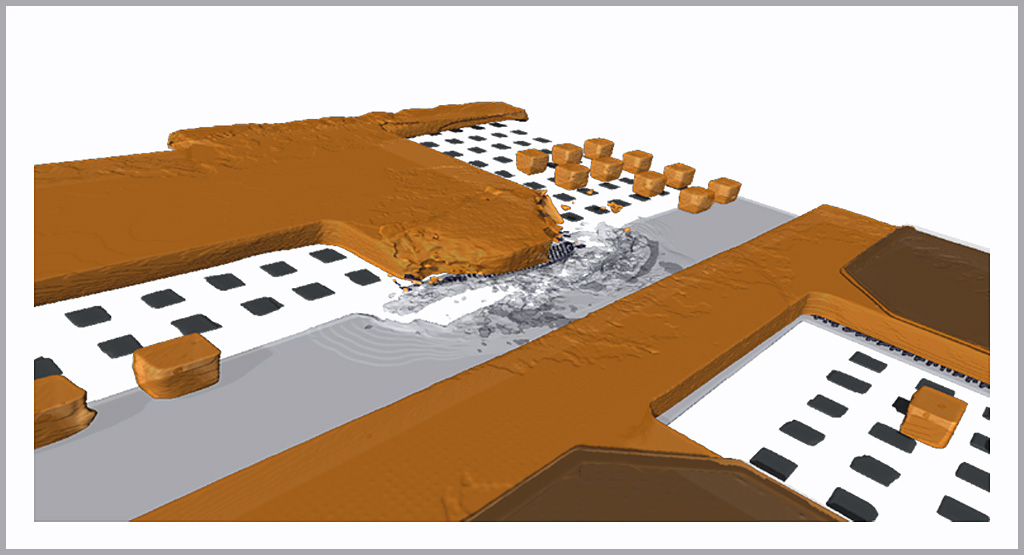

Mittels Power Temperature Cycling Tests soll etwa herausgefunden werden, ob die Bauteile auch unter Ausnahmezuständen weiterhin zuverlässig funktionieren. Dabei erfahren die Komponenten eine periodisch auftretende Spannungsspitze, welche in lokal stark begrenzten Bereichen Temperaturanstiege von mehreren Hundert Grad Celsius zur Folge hat.

Bedingt durch die Komplexität der Bauteile, welche oftmals auch mehrere Ebenen, sogenannte Layer, umfassen, lassen sich nach einem Versagen oftmals nur schwierig Rückschlüsse auf den genauen Hergang des Ausfalls bzw. die betroffenen Einzelkomponenten ziehen. Darüber hinaus treten meist mehrere Ausfälle im Affekt auf, deren Hergang schwierig zu rekonstruieren und zu interpretieren ist.